|

|

| |

|

|

|

|

|

| |

|

|

| |

|

Introduction

|

|

|

RVM stands for Reference Verification Methodology. This was developed by Synopsys. I think this is one of the best verification methodology out there. Ofcourse we have VMM, which is same as RVM, but it is for SystemVerilog. |

| |

|

|

|

|

Before RVM came, each verification engineer use to write verification env in his own way, there was no standard way to define BFM, checkers, base objects. Even in same company and same projects, there was variations in how testbenches were written. It was difficult for other engineers to understand other engineers testbench and thus resulting in poor reuse. |

| |

|

|

|

|

RVM what it does is, it defines a framework of how things should be done, it saves lot of typing, and all the testbenches looks same. |

| |

|

|

|

|

|

| |

|

|

|

|

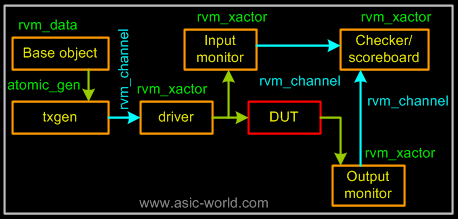

Following are important components of RVM class library |

| |

|

|

|

|

- rvm_log :Common messaging class

- rvm_data :This is used for modelling data units or base objects.

- rvm_xactor :This is used for modelling BFM, checkers, anything that requires threads

- rvm_channel :This is like FIFO, which can used for passing data from one object to another object.

- rvm_notify :This is event notification class.

- rvm_atomic_gen :This is random rvm_data generator for generating random stimulus.

- rvm_scenario_gen :This is used for generating array of random rvm_data for creating complex random stimulus.

- rvm_env :This is top level testbench, which sequences various operation in testbench.

|

| |

|

|

|

|

When you write testbench using rvm, rvm_std_lib.vrh file should be included and when compiling with rvm in VCS following command line options should be passed in addition to what you already pass |

| |

|

|

|

|

-ntb_opts rvm |

| |

|

|

| |

|

|

| |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

Copyright © 1998-2025 |

Deepak Kumar Tala - All rights reserved |

|

Do you have any Comment? mail me at:deepak@asic-world.com

|

|